# Extended Voltage Calling Number ion Identification Circuit (ECNIC)

#### **Features**

- 1200 baud BELL 202 and CCITT V.23

Frequency Shift Keying (FSK) demodulation

- Compatible with Bellcore GR-30-CORE and SR-TSV-002476

- High input sensitivity: -36dBm minimum FSK Detection Level

- Simple serial 3-wire data interface eliminating the need for a UART

- · Power down mode

- Internal gain adjustable amplifier

- · Carrier detect status output

- Uses 3.579545 MHz crystal

- 2.7 5.5V operation

- Low power CMOS technology

## **Applications**

- Calling Number Delivery (CND), Calling Name Delivery (CNAM) and Calling Identity on Call Waiting (CIDCW) features of Bellcore CLASS<sup>SM</sup> service

- Feature phones

- Phone sets, adjunct boxes

- FAX machines

- Telephone answering machines

- Database query systems

- Battery powered applications

ISSUE 2 July 1996

#### **Ordering Information**

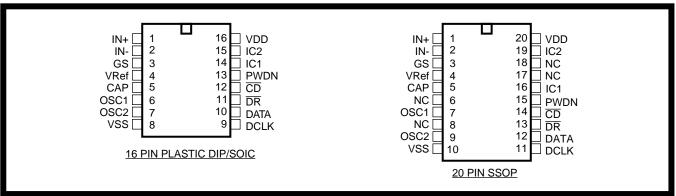

MT88E41AE 16 Pin Plastic DIP MT88E41AS 16 Pin SOIC MT88E41AN 20 Pin SSOP -40 °C to +85 °C

### Description

The MT88E41 Extended Voltage Calling Number Identification Circuit (ECNIC) is a CMOS integrated circuit providing an interface to various calling line information delivery services that utilize 1200 baud BELL 202 or CCITT V.23 FSK voiceband data transmission schemes. The ECNIC receives and demodulates the signal and outputs data into a simple 3-wire serial interface.

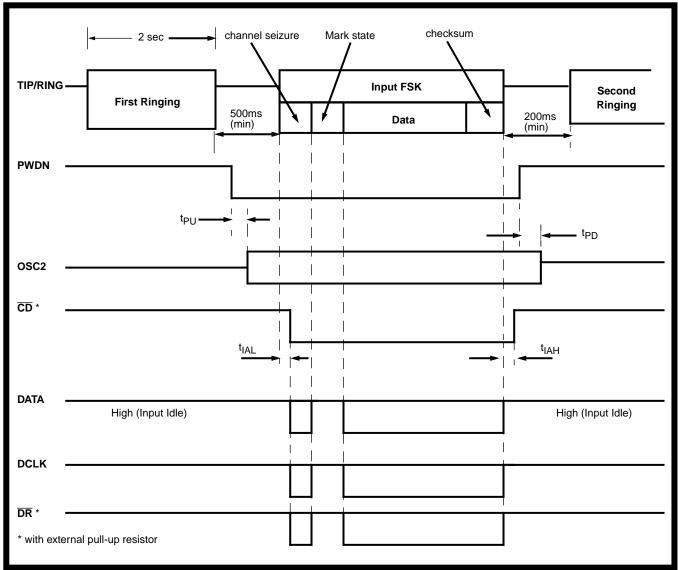

Typically, the FSK modulated data containing information on the calling line is sent before alerting the called party or during the silent interval between the first and second ring using either CCITT V.23 recommendations or Bell 202 specifications.

The ECNIC accepts and demodulates both CCITT V.23 and BELL 202 signals. Along with serial data and clock, the ECNIC provides a data ready signal to indicate the reception of every 8-bit character sent from the Central Office. The received data can be processed externally by a microcontroller, stored in memory, or displayed as is, depending on the application.

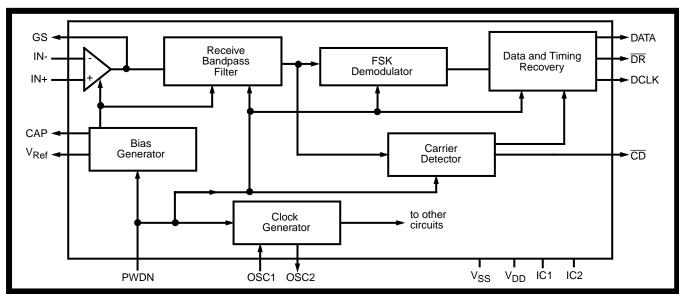

Figure 1 - Functional Block Diagram

Figure 2 - Pin Connections

# **Pin Description**

| Piı | n #              |                  | <b>5</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  | 20               | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1   | 1                | IN+              | Non-inverting Op-Amp (Input).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2   | 2                | IN-              | Inverting Op-Amp (Input).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3   | 3                | GS               | Gain Select (Output). Gives access to op-amp output for connection of feedback resistor.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4   | 4                | V <sub>Ref</sub> | Voltage Reference (Output). Nominally V <sub>DD/2</sub> . This is used to bias the op-amp inputs.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5   | 5                | CAP              | Capacitor. Connect a 0.1μF capacitor to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6   | 7                | OSC1             | Oscillator (Input). Crystal connection. This pin can be driven directly from an external clocking source.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7   | 9                | OSC2             | Oscillator (Output). Crystal connection. When OSC1 is driven by an external clock, this pin should be left open.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8   | 10               | V <sub>SS</sub>  | Power supply ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

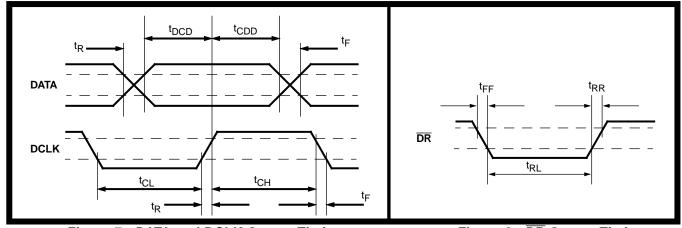

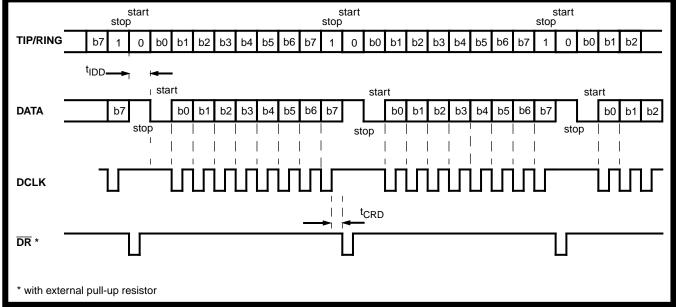

| 9   | 11               | DCLK             | <b>Data Clock (Output).</b> Outputs a clock burst of 8 low going pulses at 1202.8Hz (3.5795MHz divided by 2976). Every clock burst is initiated by the DATA stop bit start bit sequence. When the input DATA is 1202.8 baud, the positive edge of each DCLK pulse coincides with the middle of the data bits output at the DATA pin. No DCLK pulses are generated during the start or stop bits. Typically, DCLK is used to clock the eight data bits from the 10 bit data word into a serial-to-parallel converter. |

| 10  | 12               | DATA             | <b>Data (Output).</b> Serial data output corresponding to the FSK input and switching at the input baud rate. Mark frequency at the input corresponds to a logic high, while space frequency corresponds to a logic low at the DATA output. With no FSK input, DATA is at logic high. This output stays high until $\overline{\text{CD}}$ has become active.                                                                                                                                                         |

| 11  | 13               | DR               | <b>Data Ready (Open Drain Output).</b> This output goes low after the last DCLK pulse of each word. This can be used to identify the data (8-bit word) boundary on the serial output stream. Typically, $\overline{DR}$ is used to latch the eight data bits from the serial-to-parallel converter into a microcontroller.                                                                                                                                                                                           |

| 12  | 14               | CD               | Carrier Detect (Open Drain Output). A logic low indicates that a carrier has been present for a specified time on the line. A time hysteresis is provided to allow for momentary discontinuity of carrier.                                                                                                                                                                                                                                                                                                           |

| 13  | 15               | PWDN             | <b>Power Down (Input).</b> Active high, Schmitt Trigger input. Powers down the device including the input op-amp and the oscillator.                                                                                                                                                                                                                                                                                                                                                                                 |

| 14  | 16               | IC1              | Internal Connection 1. Connect to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15  | 19               | IC2              | Internal Connection 2. Internally connected, leave open circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16  | 20               | $V_{DD}$         | Positive power supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 6,8<br>17,<br>18 | NC               | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## **Functional Description**

The MT88E41 Extended Voltage Calling Number Identification Circuit (ECNIC) is a device compatible with the Bellcore proposal (GR-30-CORE) on generic requirements for transmitting asynchronous voiceband data to Customer Premises Equipment (CPE) from a serving Stored Program Controlled Switching System (SPCS) or a Central Office (CO). This data transmission technique is applicable in a variety of services like Calling Number Delivery (CND), Calling Name Delivery (CNAM) or Calling Identity Delivery on Call Waiting (CIDCW) as specified in Custom Local Area Signalling Service (CLASS<sup>SM</sup>) calling information delivery features by Bellcore.

With CND, CNAM and CIDCW service, the called subscriber has the capability to display or to store the information on the calling party which is sent by the CO and received by the ECNIC.

In the CND service, information about a calling party is embedded in the silent interval between the first and second ring. During this period, the ECNIC receives and demodulates the 1200 baud FSK signal (compatible with Bell-202 specification) and outputs data into a 3-wire serial interface.

In the CIDCW service, information about a second calling party is sent to the subscriber, (while the subscriber is engaged in another call). During this period, the ECNIC receives and demodulates the FSK signal as in the CND case.

The ECNIC is designed to provide the data transmission interface required for the above service

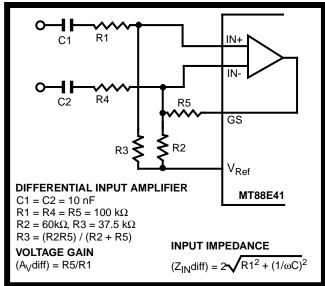

Figure 3 - Differential Input Configuration

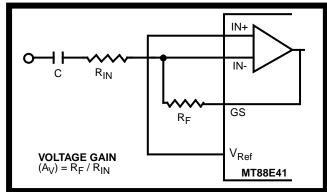

Figure 4 - Single-Ended Input Configuration

at the called subscriber location either in the on-hook case as in CND, or the off-hook case, as in CIDCW. The functional block diagram of the ECNIC is shown in Figure 1. Note however, for CIDCW applications, a separate CAS (CPE Alerting Signal) detector is required.

In Europe, Caller ID and CIDCW services are being proposed. These schemes may be different from their North American counterparts. In most cases, 1200 baud CCITT V.23 FSK is used instead of Bell 202. Because the ECNIC can also demodulate 1200 baud CCITT V.23 with the same performance, it is suitable for these applications.

Although the main application of the ECNIC is to support CND and CIDCW service, it may also be used in any application where 1200 baud Bell 202 and/or CCITT V.23 FSK data reception is required.

#### **Input Configuration**

The input arrangement of the MT88E41 provides an operational amplifier, as well as a bias source ( $V_{Ref}$ ) which is used to bias the inputs at  $V_{DD/2}$ . Provision is made for connection of a feedback resistor to the opamp output (GS) for adjustment of gain. In a single-ended configuration, the input pins are connected as shown in Figure 4.

Figure 3 shows the necessary connections for a differential input configuration.

#### **User Interface**

The ECNIC provides a powerful 3-pin interface which can reduce the external hardware and software requirements. The ECNIC receives the FSK signal, demodulates it, and outputs the extracted data to the DATA pin. For each received stop bit start bit sequence, the ECNIC outputs a fixed frequency clock string of 8 pulses at the DCLK pin. Each clock

rising edge corresponds to the centre of each DATA bit cell (providing the incoming baud rate matches the DCLK rate). DCLK is not generated for the stop and start bits. Consequently, DCLK will clock only valid data into a peripheral device such as a serial to parallel shift register or a micro-controller. The ECNIC also outputs an end of word pulse (data ready) at the  $\overline{\rm DR}$  pin. The data ready signal indicates the reception of every 10-bit word sent from the Central Office. This output is typically used to interrupt a micro-controller. The three outputs together, eliminate the need for a UART (Universal Asynchronous Receiver Transmitter) or the high software overhead of performing the UART function (asynchronous serial data reception).

Note that the 3-pin interface may also output data generated by voice since these frequencies are in the input frequency detection band of the device. The user may choose to ignore these outputs when FSK data is not expected, or force the ECNIC into its powerdown mode.

#### **Power Down Mode**

For applications requiring reduced power consumption, the ECNIC can be forced into power down when it is not needed to receive FSK data. This is done by pulling the PWDN pin high. In powerdown mode, the crystal oscillator, op-amp and internal circuitry are all disabled and the ECNIC will not react to the input signal. DATA and DCLK are at logic high, and  $\overline{DR}$  and  $\overline{CD}$  are at high impedance or at logic high when pulled up with resistors.The ECNIC can be awakened for reception of the FSK signal by pulling the PWDN pin to ground (see Figure 9).

#### **Carrier Detect**

The presence of the FSK signal is indicated by a logic low at the carrier detect ( $\overline{\text{CD}}$ ) output. This output has built in hysteresis to prevent toggling when the received signal is shortly interrupted. Note that the  $\overline{\text{CD}}$  output is also activated by voice since these frequencies are in the input frequency detection band of the device. The user may choose to ignore this output when FSK data is not expected, or force the ECNIC into its powerdown mode.

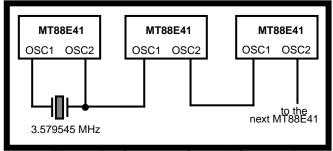

Figure 5 - Common Crystal Connection

#### **Crystal Oscillator**

The ECNIC uses a crystal oscillator as the master timing source for filters and the FSK demodulator. The crystal specification is as follows:

Frequency: 3.579545 MHz

Frequency tolerance: ±0.1%(-40°C+85°C)

Resonance mode: Parallel

Load capacitance: 18 pF

Maximum series resistance: 150 ohms

Maximum drive level (mW): 2 mW

e.g. CTS MP036S

A number of MT88E41 devices can be connected as shown in Figure 5 such that only one crystal is required. The connection between OSC2 and OSC1 can be D.C. coupled as shown, or A.C. coupled using 30pF capacitors. Alternatively, the OSC1 inputs on all devices can be driven from a CMOS buffer (dc coupled) with the OSC2 outputs left unconnected.

#### **VRef and CAP Inputs**

$V_{Ref}$  is the output of a low impedance voltage source equal to  $V_{DD/2}$  and is used to bias the input op-amp. A 0.1 $\mu$ F capacitor is required between CAP and  $V_{SS}$  to suppress noise on  $V_{Ref.}$

## **Applications**

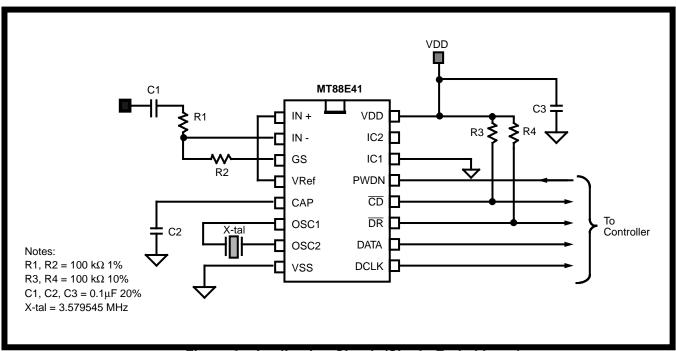

The circuit shown in Figure 6 illustrates the use of the MT88E41 device in a typical FSK receiver system. Bellcore Special Report SR-TSV-002476 specifies that the FSK receiver should be able to receive FSK signal levels as follows:

Received Signal Level at 1200Hz: -32dBm to -12dBm

Received Signal Level at 2200Hz: -36dBm to -12dBm

This condition can be attained by choosing suitable values of R1 and R2. The MT88E41 configured in a unity gain mode as shown in Fig. 6 meets the above level requirements.

For applications requiring detection of lower FSK signal level, the input op amp may be configured to provide adequate gain.

Figure 6 - Application Circuit (Single-Ended Input)

# $\textbf{Absolute Maximum Ratings*} \text{ - Voltages are with respect to V}_{\text{SS}} \text{ unless otherwise stated.}$

|   | Parameter                                                        | Symbol           | Min  | Max                  | Units |

|---|------------------------------------------------------------------|------------------|------|----------------------|-------|

| 1 | DC Power Supply Voltage V <sub>DD</sub> to V <sub>SS</sub>       | $V_{DD}$         | -0.3 | 6                    | V     |

| 2 | Voltage on any pin                                               | $V_{P}$          | -0.3 | V <sub>DD</sub> +0.3 | V     |

| 3 | Current at any pin (except V <sub>DD</sub> and V <sub>SS</sub> ) | I <sub>I/O</sub> |      | ±10                  | mA    |

| 4 | Storage Temperature                                              | T <sub>ST</sub>  | -65  | +150                 | °C    |

| 5 | Package Power Dissipation                                        | P <sub>D</sub>   |      | 500                  | mW    |

<sup>\*</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

# Recommended Operating Conditions - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated

|   | Characteristics              | Sym              | Min | Тур      | Max  | Units | Test Conditions |

|---|------------------------------|------------------|-----|----------|------|-------|-----------------|

| 1 | DC Power Supply Voltage      | $V_{DD}$         | 2.7 |          | 5.5  | V     |                 |

| 2 | Clock Frequency              | f <sub>OSC</sub> |     | 3.579545 |      | MHz   |                 |

| 3 | Tolerance on Clock Frequency | Δfc              |     |          | ±0.1 | %     |                 |

| 4 | Operating Temperature        |                  | -40 |          | +85  | °C    |                 |

## DC Electrical Characteristics<sup>†</sup>

|   |              | Characteristics                                             | Sym                                | Min                                          | Тур*    | Max                                          | Units    | Test<br>Conditions                               |

|---|--------------|-------------------------------------------------------------|------------------------------------|----------------------------------------------|---------|----------------------------------------------|----------|--------------------------------------------------|

| 1 | S U P        | Standby Supply Current $V_{DD}$ =2.7V $V_{DD}$ =5.5V        | I <sub>DDQ</sub>                   |                                              | 7<br>15 | 14<br>28                                     | μΑ<br>μΑ | PWDN=V <sub>DD</sub>                             |

| 2 | P<br>L<br>Y  | Operating Supply Current $V_{DD}$ =2.7V $V_{DD}$ =5.5V      | I <sub>DD</sub>                    |                                              | 1 3     | 2<br>5                                       | mA<br>mA | PWDN=V <sub>SS</sub>                             |

| 3 | DATA<br>DCLK | Low Level Output Voltage<br>High Level Output Voltage       | $V_{OL}$                           | V <sub>DD</sub> -0.4                         |         | 0.4                                          | V        | I <sub>OL</sub> =2.5mA<br>I <sub>OH</sub> =0.8mA |

| 4 | DR<br>CD     | Sink Current                                                | I <sub>OL</sub>                    | 2.5                                          |         |                                              | mA       | V <sub>OL</sub> =0.4V                            |

| 5 | PWDN         | Schmitt Input High Threshold<br>Schmitt Input Low Threshold | V <sub>T+</sub><br>V <sub>T-</sub> | 0.48*V <sub>DD</sub><br>0.28*V <sub>DD</sub> |         | 0.68*V <sub>DD</sub><br>0.48*V <sub>DD</sub> | V        |                                                  |

| 6 |              | Schmitt Hysterisis                                          | $V_{HYS}$                          | 0.2                                          |         |                                              | V        |                                                  |

| 7 |              | Input Current                                               | I <sub>IN</sub>                    |                                              |         | 10                                           | μΑ       | $V_{SS} \le V_{IN} \le V_{DD}$                   |

| 8 | VRef         | Output Voltage                                              | $V_{Ref}$                          | 0.5V <sub>DD</sub> - 0.05                    |         | $0.5V_{DD} + 0.05$                           | V        | No Load                                          |

| 9 | vicei        | Output Resistance                                           |                                    |                                              |         | 2                                            | kΩ       |                                                  |

<sup>†</sup> DC Electrical Characteristics are over recommended operating conditions unless otherwise stated. \* Typical figures are at 25°C and are for design aid only.

# Electrical Characteristics<sup>†</sup> - Gain Setting Amplifier

|    | Characteristics              | Sym              | Min | Typ <sup>‡</sup> | Max                  | Units     | Test Conditions                      |

|----|------------------------------|------------------|-----|------------------|----------------------|-----------|--------------------------------------|

| 1  | Input Leakage Current        | I <sub>IN</sub>  |     |                  | 1                    | μΑ        | $V_{SS} \le V_{IN} \le V_{DD}$       |

| 2  | Input Resistance             | R <sub>in</sub>  | 5   |                  |                      | $M\Omega$ |                                      |

| 3  | Input Offset Voltage         | Vos              |     |                  | 25                   | mV        |                                      |

| 4  | Power Supply Rejection Ratio | PSRR             | 30  | 40               |                      | dB        | 1kHz ripple on V <sub>DD</sub>       |

| 5  | Common Mode Rejection        | CMRR             | 30  | 40               |                      | dB        | $V_{CMmin} \le V_{IN} \le V_{CMmax}$ |

| 6  | DC Open Loop Voltage Gain    | A <sub>VOL</sub> | 30  | 32               |                      | dB        |                                      |

| 7  | Unity Gain Bandwidth         | f <sub>C</sub>   | .2  | 0.3              |                      | MHz       |                                      |

| 8  | Output Voltage Swing         | Vo               | 0.5 |                  | V <sub>DD</sub> -0.5 | $V_{pp}$  | Load ≥ 50kΩ                          |

| 9  | Maximum Capacitive Load (GS) | C <sub>L</sub>   |     |                  | 100                  | pF        |                                      |

| 10 | Maximum Resistive Load (GS)  | R <sub>L</sub>   | 50  |                  |                      | kΩ        |                                      |

| 11 | Common Mode Range Voltage    | V <sub>CM</sub>  | 1.0 |                  | V <sub>DD</sub> -1.0 | V         |                                      |

## AC Electrical Characteristics<sup>†</sup> - FSK Detection

|   | Characteristics                                                      | Sym | Min              | Typ <sup>‡</sup> | Max              | Units     | Notes*                   |

|---|----------------------------------------------------------------------|-----|------------------|------------------|------------------|-----------|--------------------------|

| 1 | Input Detection Level                                                |     | -36<br>12.3      |                  | -9<br>275        | dBm<br>mV | 1, 2, 3<br>1, 2, 3       |

| 2 | Input Baud Rate                                                      |     | 1188             | 1200             | 1212             | baud      | 7                        |

| 3 | Input Frequency Detection<br>Bell 202 1 (Mark)<br>Bell 202 0 (Space) |     | 1188<br>2178     | 1200<br>2200     | 1212<br>2222     | Hz<br>Hz  | }7 BELL 202 Frequencies  |

|   | CCITT V.23 1 (Mark)<br>CCITT V.23 0 (Space)                          |     | 1280.5<br>2068.5 | 1300<br>2100     | 1319.5<br>2131.5 | Hz<br>Hz  | 7 CCITT V.23 Frequencies |

| 4 | Input Noise Tolerance 20 log(signal) noise                           | SNR | 20               |                  |                  | dB        | 2, 3, 4, 5               |

<sup>†</sup> Electrical characteristics are over recommended operating conditions, unless otherwise stated. ‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

<sup>†</sup> AC Electrical Characteristics are over recommended operating conditions, unless otherwise stated. ‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

# AC Electrical Characteristics<sup>†</sup> - Timing

|    |            | Characteristics                                | Sym              | Min  | Typ <sup>‡</sup> | Max  | Units | Notes*   |

|----|------------|------------------------------------------------|------------------|------|------------------|------|-------|----------|

| 1  | PWDN       | Power-up time                                  | t <sub>PU</sub>  |      | 35               | 50   | ms    |          |

| 2  | OSC1       | Power-down time                                | t <sub>PD</sub>  |      | 100              | 1000 | μs    | 11       |

| 3  |            | Input FSK to $\overline{\text{CD}}$ low delay  | t <sub>IAL</sub> |      |                  | 25   | ms    |          |

| 4  | CD         | Input FSK to $\overline{\text{CD}}$ high delay | t <sub>IAH</sub> | 8    |                  |      | ms    |          |

| 5  |            | Hysteresis                                     |                  | 8    |                  |      | ms    |          |

| 6  | DATA       | Rate                                           |                  | 1188 | 1200             | 1212 | bps   | 6,12     |

| 7  |            | Input FSK to DATA delay                        | t <sub>IDD</sub> |      | 1                | 5    | ms    |          |

| 8  |            | Rise time                                      | t <sub>R</sub>   |      |                  | 200  | ns    | 8        |

| 9  | DATA       | Fall time                                      | t <sub>F</sub>   |      |                  | 200  | ns    | 8        |

| 10 | DCLK       | DATA to DCLK delay                             | t <sub>DCD</sub> | 6    | 416              |      | μs    | 6, 7, 10 |

| 11 |            | DCLK to DATA delay                             | t <sub>CDD</sub> | 6    | 416              |      | μs    | 6, 7, 10 |

| 12 |            | Frequency                                      |                  | 1200 | 1202.8           | 1205 | Hz    | 7        |

| 13 | DCLK       | High time                                      | t <sub>CH</sub>  | 415  | 416              | 417  | μs    | 7        |

| 14 |            | Low time                                       | t <sub>CL</sub>  | 415  | 416              | 417  | μs    | 7        |

| 15 | DCLK<br>DR | DCLK to $\overline{DR}$ delay                  | t <sub>CRD</sub> | 415  | 416              | 417  | μs    | 7        |

| 16 |            | Rise time                                      | t <sub>RR</sub>  |      |                  | 10   | μs    | 9        |

| 17 | DR         | Fall time                                      | t <sub>FF</sub>  |      |                  | 200  | ns    | 9        |

| 18 |            | Low time                                       | t <sub>RL</sub>  | 415  | 416              | 417  | μs    | 7        |

- † AC Electrical Characteristics are over recommended operating conditions unless otherwise stated.

- ‡ Typical figures are at 25°C and are for design aid only, not guaranteed and not subject to production testing. \*Notes:

- dBm=decibels above or below a reference power of 1mW into 600Ω.

- Using unity gain test circuit shown in Figure 6.

Mark and Space frequencies have the same amplitude.

- Band limited random noise (200-3200Hz).

- Referenced to the minimum input detection level.

- FSK input data at 1200 ±12 baud.

- OSC1 at 3.579545 MHz ±0.2%.

- 2. 3. 4. 5. 6. 7. 8. 9.

- 10k to  $V_{SS}$ , 50pF to  $V_{SS}$ . 10k to  $V_{DD}$ , 50pF to  $V_{SS}$ . Function of signal condition. 10.

- The device will stop functioning within this time, but more time may be required to reach I<sub>DDQ</sub>. For a repeating mark space sequence, the data stream will typically have equal 1 and 0 bit durations.

Figure 7 - DATA and DCLK Output Timing

Figure 8 - DR Output Timing

Figure 9 - Input and Output Timing (Bellcore CND Service)

Figure 10 - Serial Data Interface Timing

Notes: